X20CM4800X - Data sheet V1.04

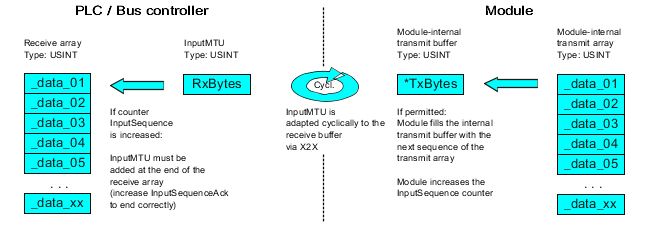

When receiving data, the transmit array is generated by the module, transferred via Flatstream and must then be reproduced in the receive array. The structure of the incoming data stream can be set with the mode register. The algorithm for receiving the data does not change in this regard.

Fig.: Flatstream communication (input)

Algorithm

|

- The CPU must monitor InputSequenceCounter. |

Cyclic checks: - The module checks InputSyncAck. - The module checks InputSequenceAck. |

Preparation: - The module forms the segments and control bytes and creates the transmit array. |

Action: - The module transfers the current element of the internal transmit array to the internal transmit buffer. - The module increases InputSequenceCounter. |

1) Receiving (as soon as InputSequenceCounter is increased): - The CPU must apply data from InputMTU and append it to the end of the receive array. - The CPU must match InputSequenceAck to InputSequenceCounter of the sequence currently being processed. |

Completion: - The module monitors InputSequenceAck. → A sequence is only considered to have been transferred successfully if it has been acknowledged via InputSequenceAck. - Subsequent sequences are only transmitted in the next bus cycle after the completion check has been carried out successfully. |

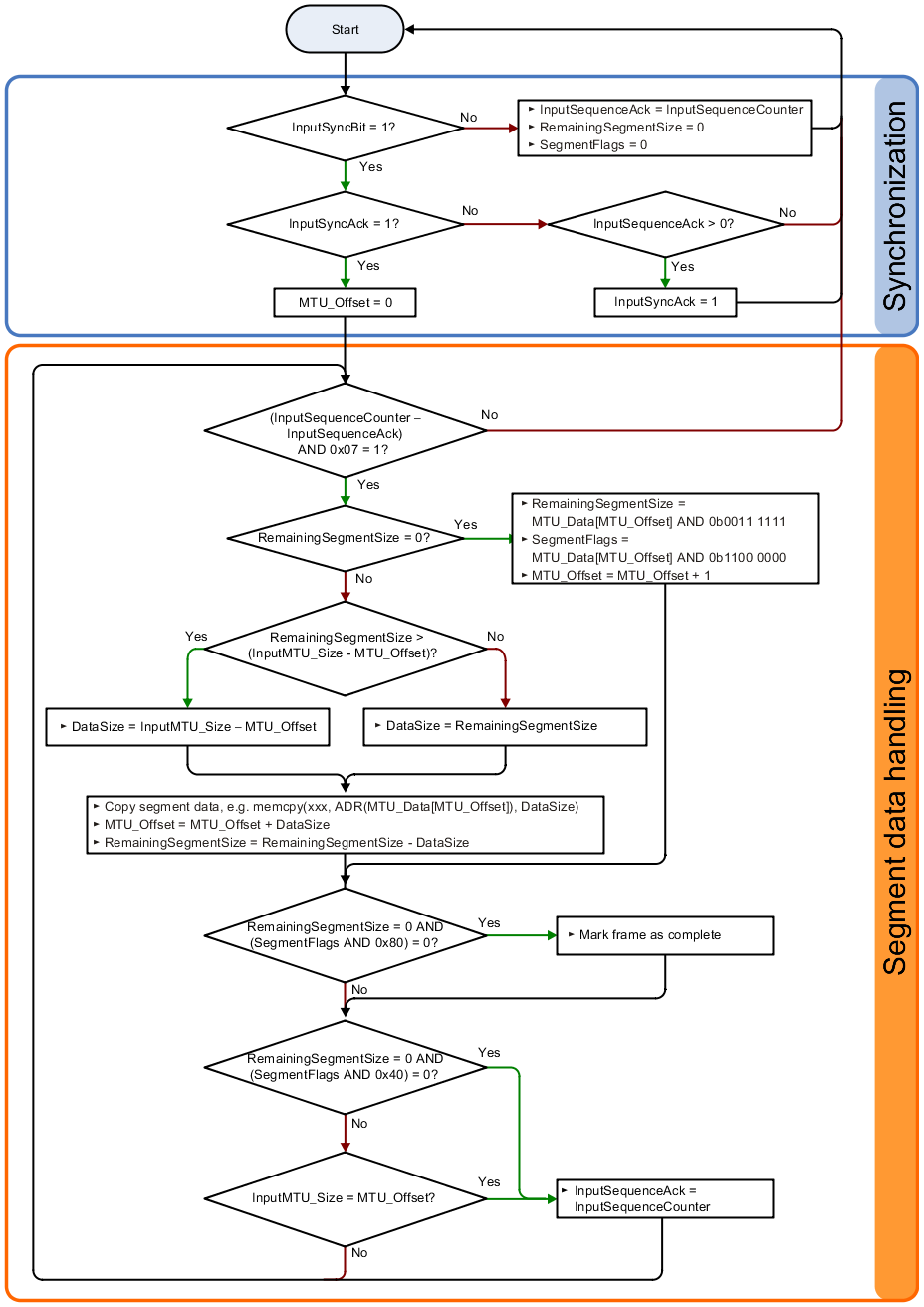

Fig.: Flow chart for the input direction