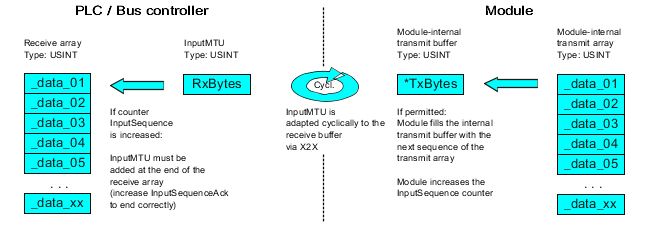

When receiving data, the transmit array is generated by the module, transferred via Flatstream and must then be reproduced in the receive array. The structure of the incoming data stream can be set with the mode register. The algorithm for receiving the data does not change in this regard.

接收数据时,发送数组由模块生成,通过Flatstream传输,然后必须在接收数组中重现。传入数据流的结构可以通过模式寄存器来设置。在这方面,接收数据的算法并没有改变。

Fig.: Flatstream communication (input)

图: Flat流通信 (输入)

Algorithm

算法

0) Cyclic status query: - The CPU must monitor InputSequenceCounter.

0) 循环状态查询: - CPU必须监测InputSequenceCounter。 |

Cyclic checks: - The module checks InputSyncAck. - The module checks InputSequenceAck.

循环检查: - 模块检查InputSyncAck。 - 模块检查InputSequenceAck。 |

Preparation: - The module forms the segments and control bytes and creates the transmit array.

准备: - 模块形成段和控制字节,并创建发送数组。 |

Action: - The module transfers the current element of the internal transmit array to the internal transmit buffer.

- The module increases InputSequenceCounter. 执行: - 模块将内部发送数组的当前元素转移到内部发送缓冲区。 - 模块增加InputSequenceCounter。 |

1) Receiving (as soon as InputSequenceCounter is increased): - The CPU must apply data from InputMTU and append it to the end of the receive array. - The CPU must match InputSequenceAck to InputSequenceCounter of the sequence currently being processed.

1) 接收(一旦InputSequenceCounter增加): - CPU必须应用InputMTU的数据,并将其追加到接收数组的末端。 - CPU必须将InputSequenceAck与当前正在处理的序列的InputSequenceCounter匹配。 |

Completion: - The module monitors InputSequenceAck. → A sequence is only considered to have been transferred successfully if it has been acknowledged via InputSequenceAck. - Subsequent sequences are only transmitted in the next bus cycle after the completion check has been carried out successfully.

完成: - 该模块监控InputSequenceAck。 → 只有当一个序列通过InputSequenceAck被确认时,才被认为是成功传输了。 - 后续的序列只有在成功进行了完成检查后,才会在下一个总线周期中传输。 |

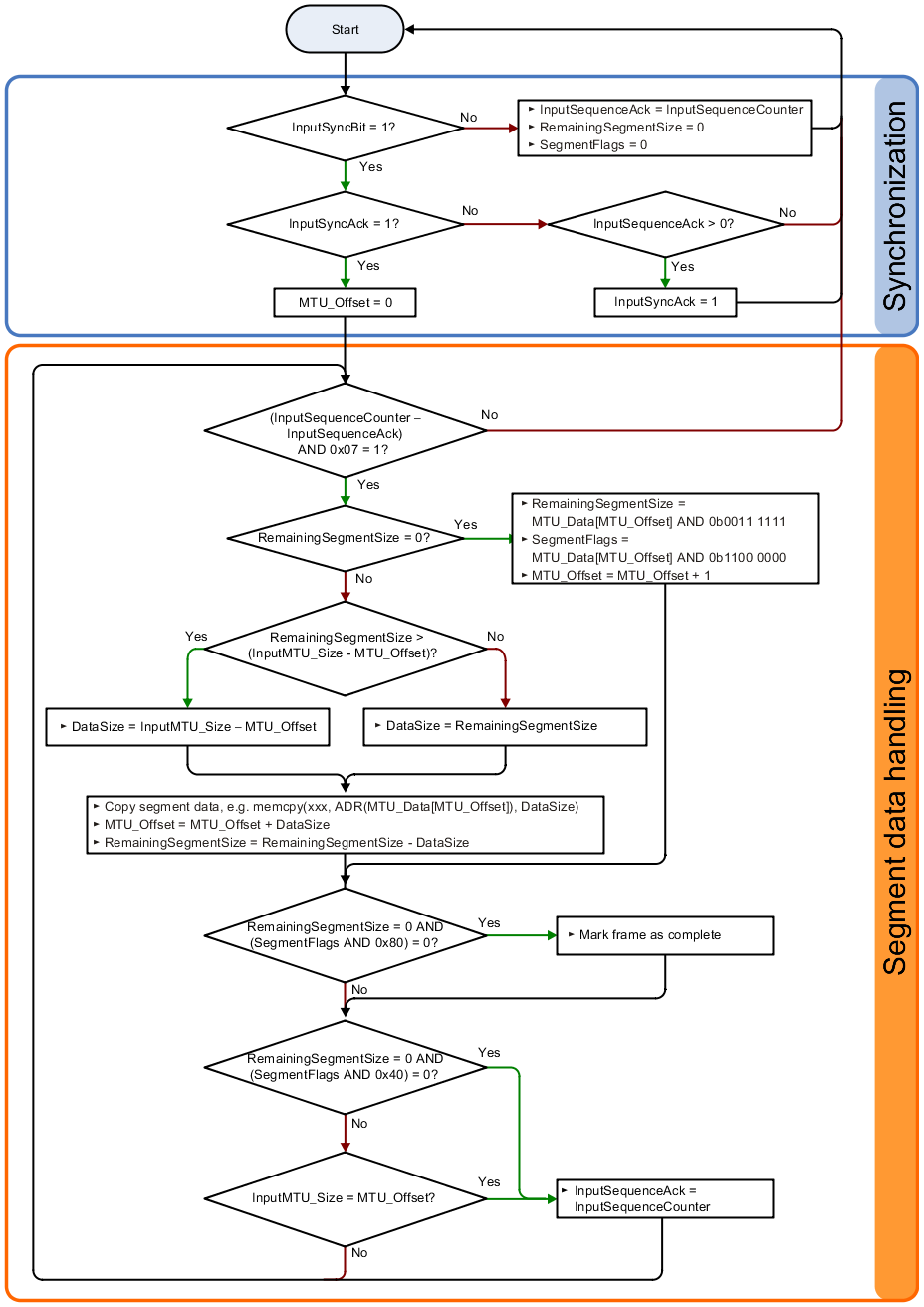

General flow chart

总体流程图

Fig.: Flow chart for the input direction

图: 输入方向的流程图