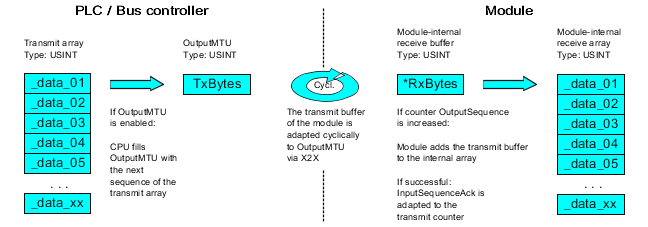

When transmitting data, the transmit array must be generated in the application program. Sequences are then transferred one by one using Flatstream and received by the module.

传输数据时,必须在应用程序中生成传输数组。然后使用Flat流逐个传输序列,并由模块接收。

Information: 注意:

Although all B&R modules with Flatstream communication always support the most compact transfers in the output direction, it is recommended to use the same design for the transfer arrays in both communication directions. 尽管所有采用Flat流通信的B&R模块在输出方向上总是支持最紧凑的传输,但建议在两个通信方向上使用相同设计的传输序列。 |

Fig.: Flatstream communication (output)

图: Flat流通信 (输出)

Message smaller than OutputMTU

消息小于OutputMTU

The length of the message is initially smaller than OutputMTU. In this case, one sequence would be sufficient to transfer the entire message and the necessary control byte.

消息的长度最初小于OutputMTU。在这种情况下,一个序列就足以传输整个消息和必要的控制字节。

Algorithm

算法

Cyclic status query: - The module monitors OutputSequenceCounter.

循环状态查询: - 该模块监测OutputSequenceCounter。 |

|

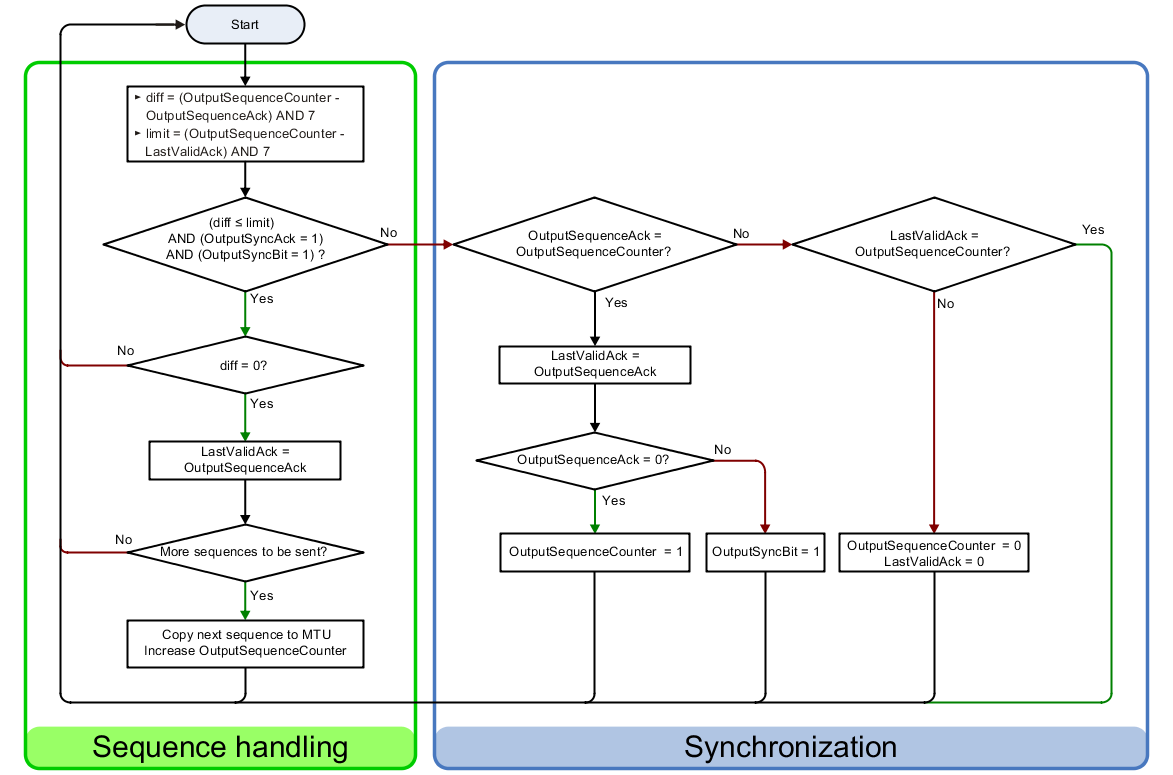

0) Cyclic checks: - The CPU must check OutputSyncAck. → If OutputSyncAck = 0: Reset OutputSyncBit and resynchronize the channel. - The CPU must check whether OutputMTU is enabled. → If OutputSequenceCounter > InputSequenceAck: MTU is not enabled because the last sequence has not yet been acknowledged.

0) 循环检查: - CPU必须检查OutputSyncAck。 → 如果OutputSyncAck = 0:重置OutputSyncBit并重新同步通道。 - CPU必须检查OutputMTU是否被启用。 → 如果OutputSequenceCounter > InputSequenceAck:MTU未启用,因为最后一个传输序列还没有被确认。 |

|

1) Preparation (create transmit array): - The CPU must split up the message into valid segments and create the necessary control bytes. - The CPU must add the segments and control bytes to the transmit array.

1)准备(创建发送数组): - CPU必须将消息分割成有效的段,并创建必要的控制字节。 - CPU必须将这些段和控制字节添加到发送数组中。 |

|

2) Transmit: - The CPU transfers the current element of the transmit array to OutputMTU. → The OutputMTU is transferred cyclically to the module's transmit buffer but not processed further. - The CPU must increase OutputSequenceCounter.

2) 传输: - CPU将发送数组的当前元素传输到OutputMTU。 → OutputMTU被循环传输到模块的发送缓冲区,但不作进一步处理。 - CPU必须增加OutputSequenceCounter。 |

|

Reaction: - The module accepts the bytes from the internal receive buffer and adds them to the internal receive array. - The module transmits acknowledgment and writes the value of OutputSequenceCounter to OutputSequenceAck.

回应: - 模块接受来自内部接收缓冲区的字节,并将其添加到内部接收数组中。 - 模块发送确认,并将OutputSequenceCounter的值写到OutputSequenceAck |

|

3) Completion: - The CPU must monitor OutputSequenceAck. → A sequence is only considered to have been transferred successfully if it has been acknowledged via OutputSequenceAck. In order to detect potential transfer errors in the last sequence as well, it is important to make sure that the length of the Completion phase is run through long enough.

.

3) 完成: - CPU必须监控OutputSequenceAck。 → 只有通过OutputSequenceAck确认序列时,才认为该序列已成功传输。为了在最后一个序列中也能检测到潜在的传输错误,重要的是要确保完成阶段的长度足够长。

|

Message larger than OutputMTU

消息大于OutputMTU

The transmit array, which must be created in the program sequence, consists of several elements. The user has to arrange the control and data bytes correctly and transfer the array elements one after the other. The transfer algorithm remains the same and is repeated starting at the point Cyclic checks.

必须在程序序列中创建的传输数组由几个元素组成,用户必须正确排列控制字节和数据字节,并一个接一个地传输数组元素。传输算法保持不变,并从循环检查点开始重复。

General flow chart

总体流程图

图: 输出方向的流程图